ВЕНТИЛЯТОР

Продукты / САПР / Приборы /

Программно-аппаратный комплекс ускорения верификации RTL

Объем проекта

до 100 млн. экв. вентилей

Объем RAM

синтезируемой части

до 400 МБит / 1U

Объем пользовательской

DRAM-памяти

до 32 ГБайт / 1U

Количество IO

до 8 тыс.

Скорость сборки проекта

до 100 млн. экв. вентилей / ч

Скорость поведенческого моделирования

до 1 МГц

Скорость получения

вейвформы

до 10 ГБит / с

Количество частотных доменов

до 100

Программно-аппаратный комплекс ускорения верификации RTL

Объем проекта

до 100 млн. экв. вентилей

Объем RAM

синтезируемой части

до 400 МБит / 1U

Объем пользовательской

DRAM-памяти

до 32 ГБайт / 1U

Объем пользовательской

DRAM-памяти

до 32 ГБайт / 1U

Количество IO

до 8 тыс.

Скорость сборки проекта

до 100 млн. экв. вентилей / ч

Скорость поведенческого моделирования

до 1 МГц

Скорость получения

вейвформы

до 10 ГБит / с

Количество частотных доменов

до 100

Программно-аппаратный комплекс ускорения верификации RTL

Объем проекта

до 100 млн. экв. вентилей

Объем RAM

синтезируемой части

до 400 МБит / 1U

Объем пользовательской

DRAM-памяти

до 32 ГБайт / 1U

Количество IO

до 8 тыс.

Скорость сборки проекта

до 100 млн. экв. вентилей / ч

Скорость поведенческого моделирования

до 1 МГц

Скорость получения

вейвформы

до 10 ГБит / с

Количество частотных доменов

до 100

Реализация

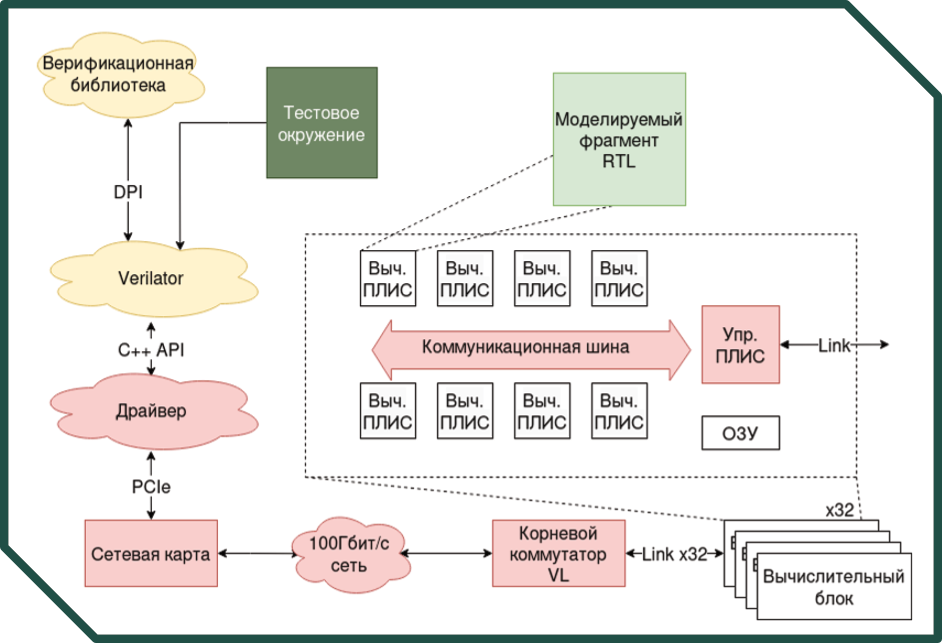

Программная

на основе open-source решений

Моделирование синтезируемой и имплементируемой части дизайна – маршрут Yosys + nextpnr.

Моделирование несинтезируемой части дизайна – компилятор Verilator.

Верификация дизайна – cocotb.

Поддерживаемые HDL языки: Verilog-2005, VHDL-2008.

Языки написания тестбенчей: Verilog-2005, SystemVerilog-2015 (с огр.), cocotb (с огр.).

Интерфейсы для подключения моделей: SystemVerilog DPI, cocotb, C++ API.

Поддержка моделирования как поведенческого RTL, так и нетлистов без задержек.

Автоматическое разделение входных HDL модулей на синтезируемые и не синтезируемые.

Синтезируемая часть дизайна разделяется на блоки, которые синхронизируются раз в такт.