Выпущен комплект разработчика 1.2

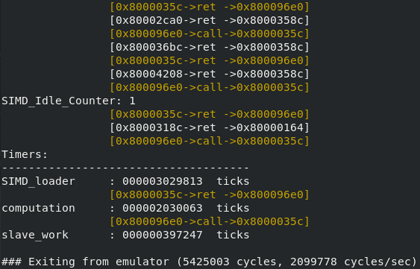

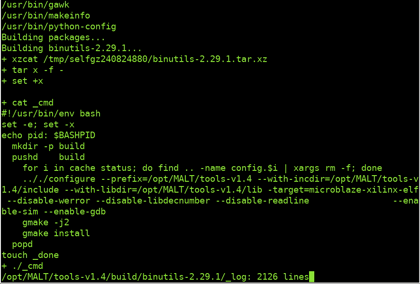

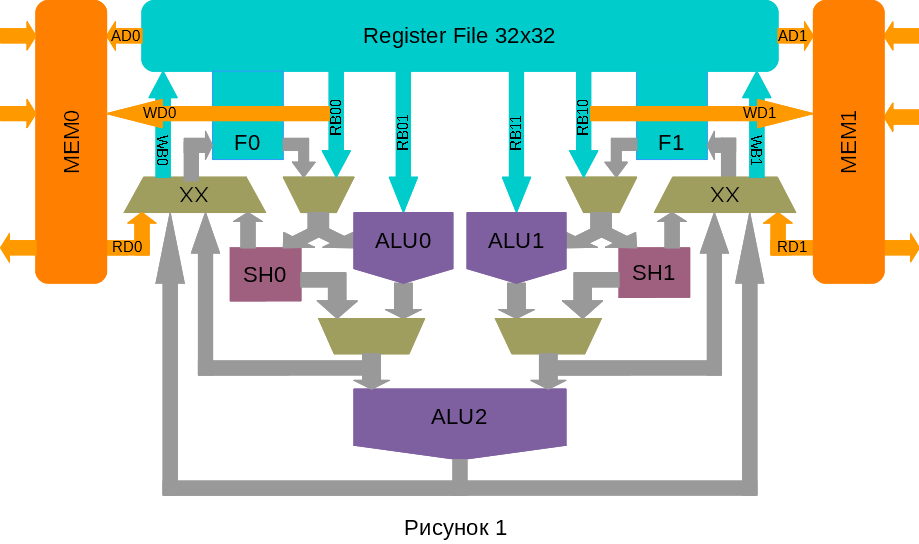

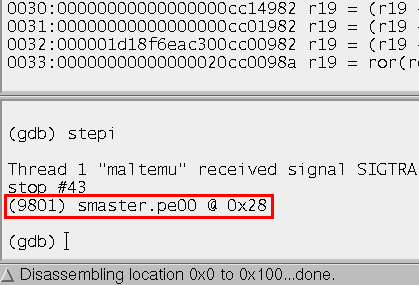

В настоящем комплекте разработчика добавлена поддержка сборки программ для тестового кристалла MALT-Cv1. Для включения режима совместимости необходимо при сборке объявить переменную окружения TASIC=1. В эмуляторе Maltemu 1.2 в функции WriteFill, ReadModify добавлены параметры rm_mod и locked. Добавлена поддержка работы с буфером интерконнекта переменной длины. Для ОС Linux и FreeBSD реализованы процедуры расчета максимально допустимого параллелизма при сборке необходимых пакетов. Во frontend'е MALTCC добавлена опция –hw-trace, которая позволяет отслеживать вызовы функций в программе.