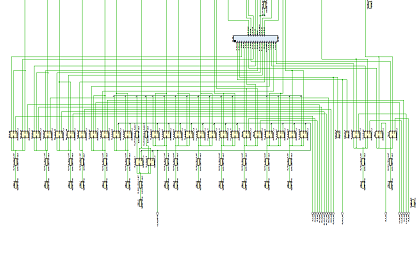

Начата разработка netlist’a процессора MALT-Cv1 в базисе TSMC 28 nm

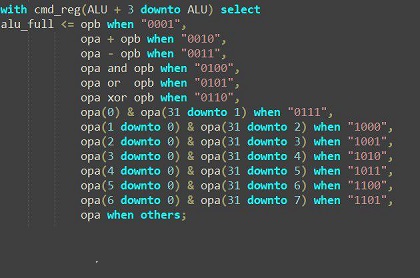

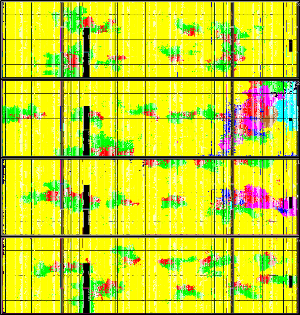

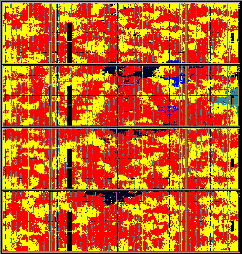

Начата разработка цифровой схемотехники (netlist) для процессора MALT-Cv1 по техпроцессу фабрики TSMC 28 nm HPC+ (high-performance computing - высокопроизводительные вычисления). Планируемая площадь кристалла - 12 мм2. Данная площадь кристалла является экономическим оптимумом для выпуска пилотной партии в рамках MPW (Multi-Project Wafer). Оценочное энергопотребление на целевой задаче составит примерно 1 Вт, что позволяет достичь значительно более высокой энергоэффективности вычислений, чем на современных центральных процессорах (CPU) и графических процессорах (GPU). Для достижения высоких показателей энергоэффективности дизайна настроен автоматизированный маршрут проектирования СБИС посредством САПР Cadence Genus synthesys solution и Cadence Incisive Enterprise Simulator, позволяющий вскоре после правок RTL получать оценки энергетики на реальной переключательной активности триггеров.